Layouts of a test chip for evaluating symmetrical and asymmetrical

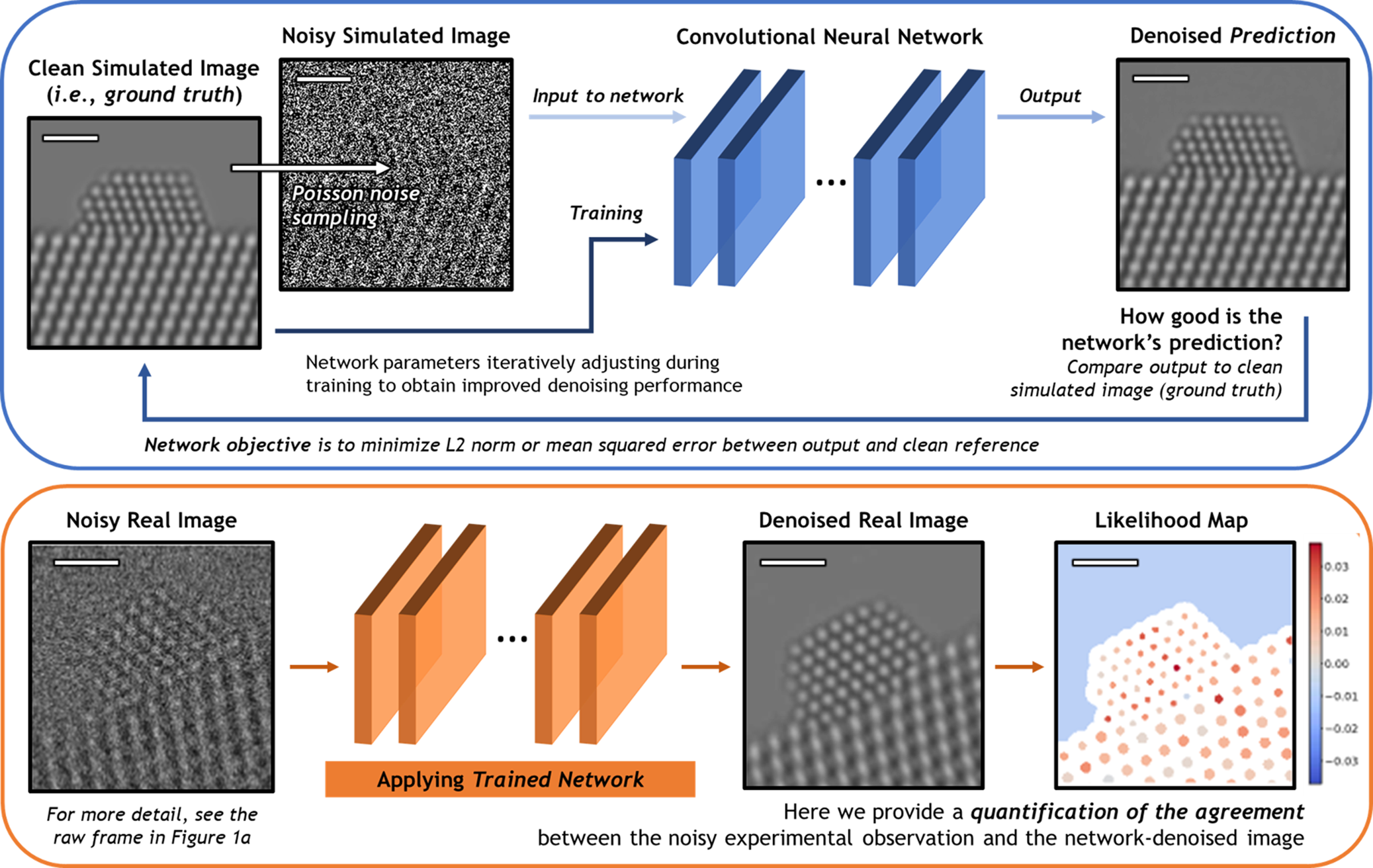

Developing and Evaluating Deep Neural Network-Based Denoising for Nanoparticle TEM Images with Ultra-Low Signal-to-Noise, Microscopy and Microanalysis

JLPEA, Free Full-Text

Basic heater layout of Thermal Test Vehicle

Thermal Analysis and Junction Temperature Rise in Multi-Chip Modules - EEWeb

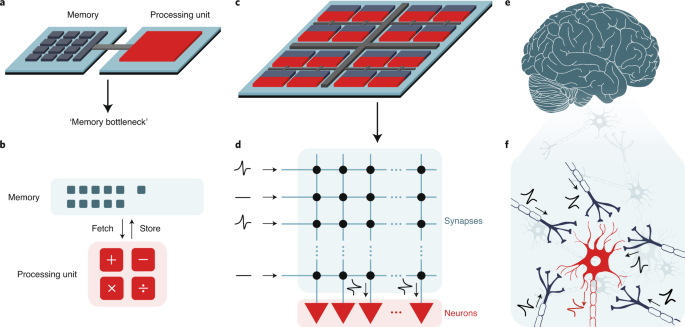

Neuro-inspired computing chips

Colour contour maps of simulated ground current in the case of bias

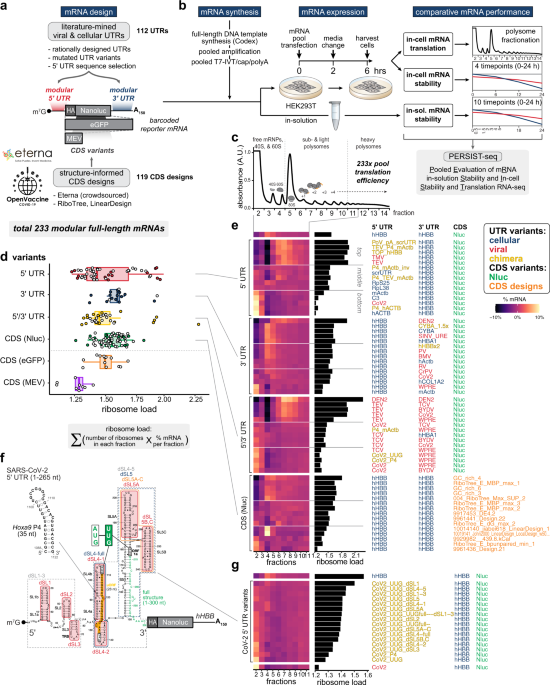

Combinatorial optimization of mRNA structure, stability, and translation for RNA-based therapeutics

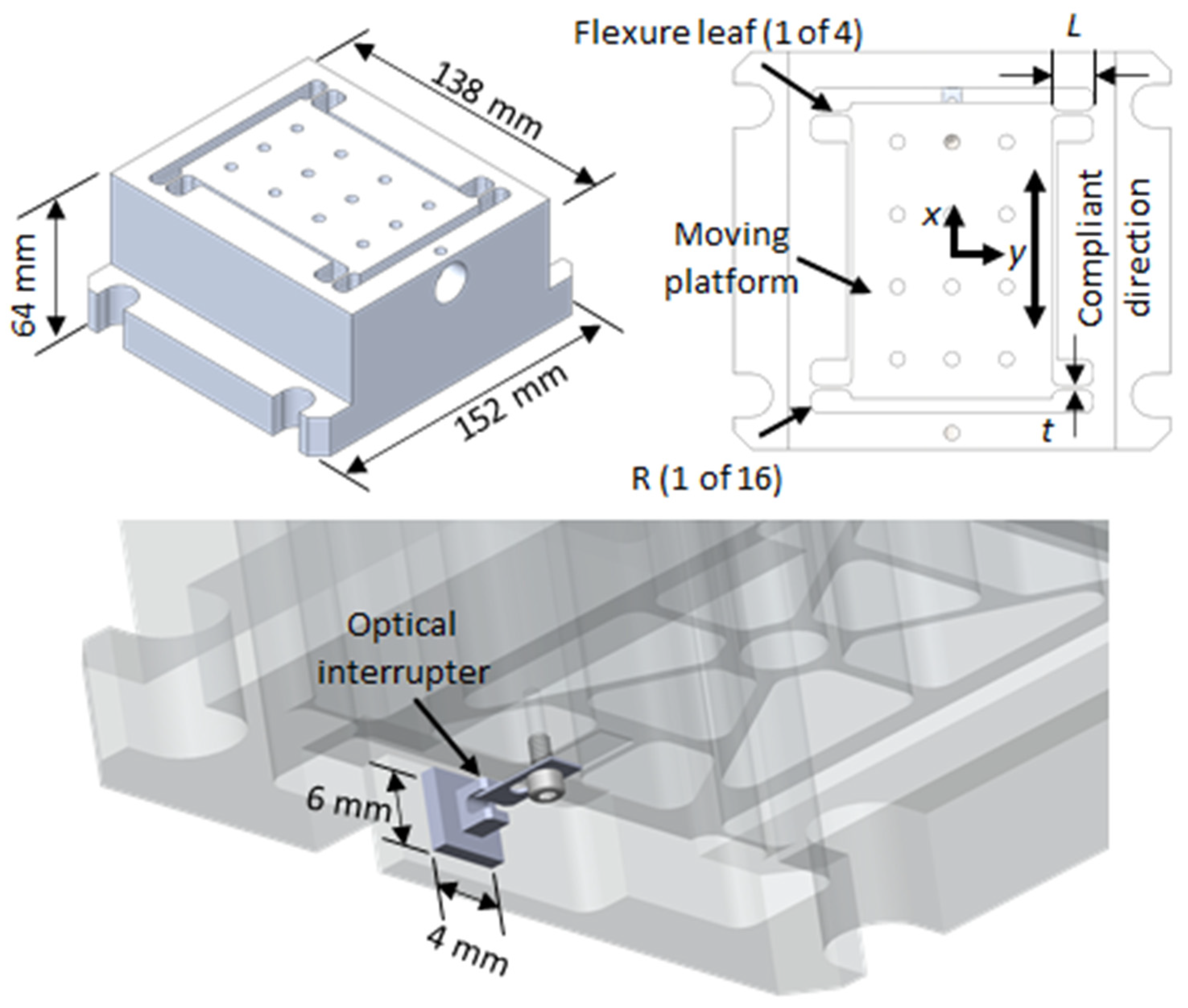

JMMP, Free Full-Text

Simulated field distribution at the wave ports of a GMSL.

Hideo SUZUKI, Yokohama National University, Yokohama, Institute of Advanced Sciences

Microfluidic chip designs to test barotactic responses. (A)

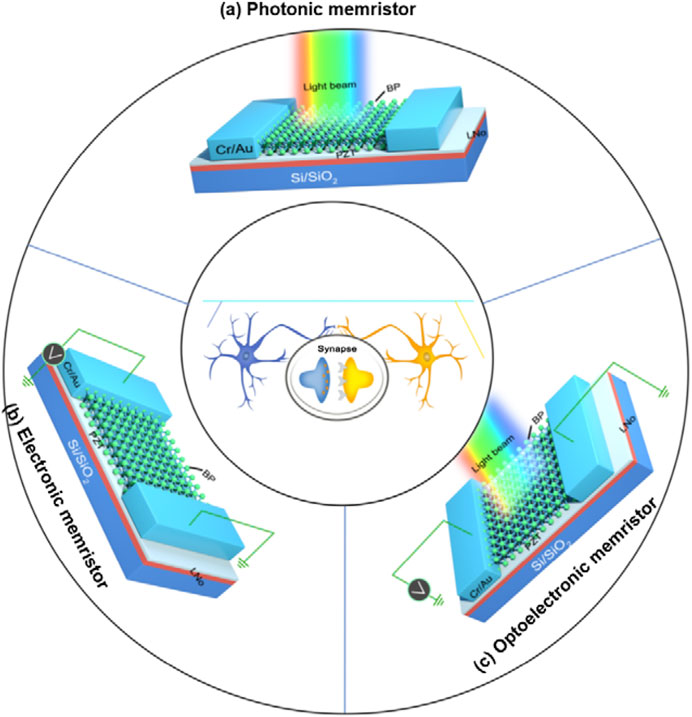

Frontiers Overview of Memristor-Based Neural Network Design and Applications

Ultra Low Power Digital CMOS Optocouplers Evaluation Board - EEWeb