PDF] Design and Fabrication of Bond Pads for Flip-Chip Bonding of

At the University of Alberta, the Imaging Science Lab aims to develop vertically-integrated (VI) CMOS image sensors with capabilities that exceed those of conventional CMOS image sensors. VI-CMOS image sensors are examples of 3D electronics because they consist of photodetectors that are placed in a layer above standard CMOS circuits. Although metal lines commonly pass over transistors in CMOS image sensors, a distinguishing characteristic of VI-CMOS image sensors is the layering of semiconductor devices. The main advantage of vertical integration is that the different layers may be fabricated using different processes, each one optimized to best suit the type of devices it contains.

A primer on 'flip chip' manufacturing techniques for smart card

Flip chip bonding, Technology introduction

Global Flip Chip Technology Market Size And Forecast 2023-2030

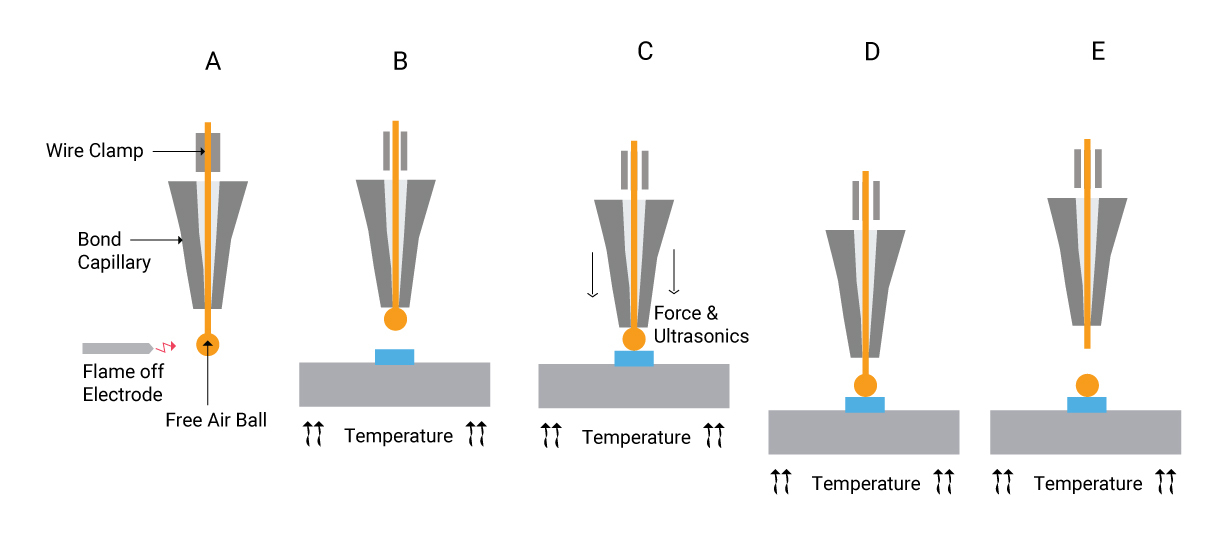

Wire Bonding: Efficient Interconnection Technique

Die Bonding, Process for Placing a Chip on a Package Substrate

Qualification of the Assembly Process of Flip-Chip BGA Packages

IC Assembly, PDF, Epoxy

PDF] Design and Fabrication of Bond Pads for Flip-Chip Bonding of

Thermosonic fine-pitch flipchip bonding of silicon chips on screen

Flip-Chip - Semiconductor Engineering

Flexible packaging of solid-state integrated circuit chips with

PDF] Design and Fabrication of Bond Pads for Flip-Chip Bonding of